The variables doesn't enter negated into the NMOS gates because NMOS turn ON for 5V. Therefore, in the lower part we have A* and B that are in parallel while C is in series. Applying to our function: we'll get F*=(A*+B)♼* Recalling the De Morgan Theorem, by negating F, AND becomes OR and viceversa. Because the high voltage level of the pass-transistor outputs is lower than the supply voltage level by the threshold. The IGFET or MOSFET is a voltage controlled field effect. The most common type of insulated gate FET which is used in many different types of electronic circuits is called the Metal Oxide Semiconductor Field Effect Transistor or MOSFET for short.

Cmos transistor diagram full#

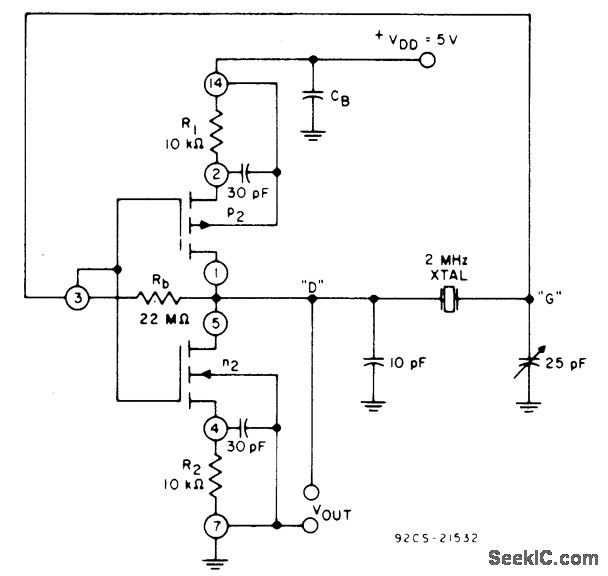

Then the lower part must implement the 0's. The schematic diagram of the CPL full adder circuit is shown in Fig 4. The MOSFET is a type of semiconductor device called an Insulated Gate Field Effect Transistor. Simulate this circuit – Schematic created using CircuitLab The variables enter negated into the PMOS gate, because the PMOS will turn ON for 0 V (and not 5 V).

Cmos transistor diagram series#

The upper part is easy (A and B* in series for AND) and C in parallel (for the OR part). I've chosen a different (and shorter function) for a simpler illustration of the method. What is the logic function implemented by the CMOS transistor network Size the NMOS and PMOS devices so that the output. When a circuit contains both NMOS and PMOS transistors we say it is implemented in CMOS. For example, let say your function is F=A♻*+C. We will now see the use of transistor for designing logic gates.

You can do this directly from the function expression. A transistor exists where a polysilicon stick crosses either an N.

This results in much better performance as it allows integrating more CMOS gates on an IC.As you know, you use the upper part of the structure (from Vout to Vcc) to set the 1's and the lower part of the structure (from Vout to Vss) to set the 0's. Drawing Stick Diagrams Mask Layout and Stick Diagram for a CMOS Inverter Transistors. Fig: D Flip flop Block Diagram D flip-flop terms into a multi-threshold CMOS technology when 1 PMOS transistor and 1 NMOS transistor are connected to the circuit of D flip-flop so the clock is high and input is low due to transistor M1 and M2 are on and M3 and M4 are off and the M5 transistor is on due to the output is low. The main advantage of CMOS is the minimal power dissipation as this only occurs during circuit switching. from publication: Using Bayesian Networks to Accurately Calculate the Reliability of Complementary. Although the circuit consists of one NMOS and one PMOS transistor, there exists a number of different design possibilities even for this very simple circuit.

Cmos transistor diagram download#

These drawbacks are minimized by using CMOS Technology. Download scientific diagram Full adder (FA) cell implemented with 28 CMOS transistors. Many modern CMOS gate circuits are buffered with additional transistor stages on their outputs. CMOS INVERTER In Fig.2.9, the mask layout design of a CMOS inverter will be examined step-by-step. The main disadvantages of NMOS technology are its electrical asymmetry and static power dissipation. CMOS or Complementary Metal Oxide Semiconductor is a combination of NMOS and PMOS transistors that operates under the applied electrical field. The main advantages of NMOS technology are simple physical process, functional density, processing speed and manufacturing efficiency. Initially, CMOS was slower and more expensive than NMOS. PMOS was then replaced by the NMOS Technology, which used to be the standard IC fabrication technology. All were powered from a 5V rail, a voltage selected to provide enough headroom for good working of the bipolar transistors. Both N and P MOSFET channels are designed to have matching characteristics.īefore CMOS, PMOS and NMOS logic were widely used for implementing logic gates. Fifty years ago, nearly all digital circuits used TTL (transistor-transistor logic) chips from the ubiquitous 74xx or 74LSxx familiesintroduced in 1964 by Texas Instruments (TI). Note that there is no difference in the construction of a transistor source and a transistor drain. A transistor exists where a polysilicon stick crosses either an N diffusion stick (NMOS transistor) or a P diffusion stick (PMOS transistor).

This technology uses both NMOS and PMOS to realize various logic functions. Mask Layout and Stick Diagram for a CMOS Inverter. Microprocessors, batteries, and digital sensors among other electronic components make use of this technology due to several key advantages.

CMOS stands for “Complementary Metal Oxide Semiconductor”. Are you wondering what is CMOS technology? CMOS technology is a predominant technology for manufacturing integrated circuits. Cut-off Region Here the operating conditions of the transistor are zero input gate voltage ( VIN ), zero drain current ID and output voltage VDS VDD.

0 kommentar(er)

0 kommentar(er)